### OPTIMIZING THE PERFORMANCE OF DIRECT DIGITAL FREQUENCY

### SYNTHESIZERS FOR LOW-POWER WIRELESS

#### COMMUNICATION SYSTEMS

By

### DAVID JAMES BETOWSKI

A thesis submitted in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE IN COMPUTER ENGINERING

WASHINGTON STATE UNIVERSITY School of Electrical Engineering and Computer Science

DECEMBER 2004

To the Faculty of Washington State University:

The members of the Committee appointed to examine the thesis of DAVID JAMES BETOWSKI find it satisfactory and recommend that it be accepted.

Chair

ii

#### ACKNOWLEDGMENT

The Author and Committee wish to extend a special thanks to those students and faculty members of the Washington State University School of Electrical Engineering and Computer Science who contributed in some way to this research:

> Daniel G. Dwyer Pao-Szu Wu Suryanarayana B. Tatapudi Jeffrey D. Lowe Parag Upadhyaya Zhihe "Bill" Zhou George S. La Rue, Ph. D. Deuk H. Heo, Ph. D.

Portions of this research were sponsored by the U.S. Air Force Research Laboratory (AFRL), the Center for the Design of Analog and Digital Integrated Circuits (CDADIC)\*, and the Center for Neural Inspired Nano-Architectures (CNINA)<sup>†</sup>.

\* www.eecs.wsu.edu/cdadic

† www.cnina.org

# OPTIMIZING THE PERFORMANCE OF DIRECT DIGITAL FREQUENCY SYNTHESIZERS FOR LOW-POWER WIRELESS

#### COMMUNICATION SYSTEMS

Abstract

by David James Betowski, M.S. Washington State University December 2004

Chair: Valeriu Beiu

A direct digital frequency synthesizer (DDFS) generates a highly accurate sine wave using feed-forward digital signal processing, overcoming many of the problems incurred with the traditional analog closed-loop frequency synthesizer, the Phase-Locked Loop (PLL). The most popular application of a DDFS is generating the variable carrier frequency required in portable wireless communication systems, which require both high accuracy and very low power consumption. A three-level abstraction analysis and design approach is presented.

The system level analysis focuses on selecting an appropriate phase-to-sine wave approximation circuit, which has traditionally been implemented with a large-sized ROM lookup table, resulting in a moderately high SFDR and very high power consumption. Recent solutions reduce the ROM size by using a segmented linear approximation to compute the sine wave in real-time. The solutions produce a very high SFDR (using up to 64 segments), but the circuit complexity remains high. A novel segmented parabolic approximation is introduced, and using only 16 segments, yields an 84 dBc SFDR. The circuit complexity is lower than other methods having a similar SFDR.

iv

Both the new approximation and the DDFS, in general, require several high-speed arithmetic components, including 8 – 32-bit adders and a Wallace-tree based multiplyaccumulate circuit. Pipelining the DDFS system may be necessary if high-speed operation is desired. A mathematical model is presented at the component level to determine the optimal number of stages with respect to the speed and power requirements.

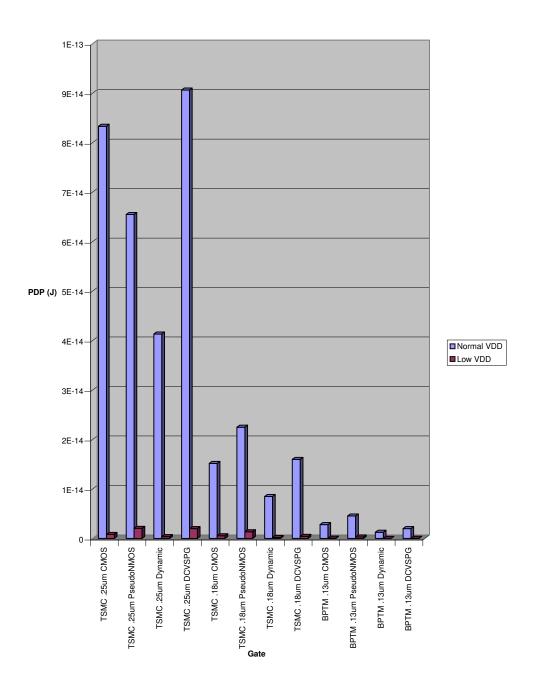

Descending to the circuit level, four logic gate styles (complementary, pseudo-NMOS, dynamic, and differential cascode voltage switch) are constructed and simulated in three different CMOS processes to analyze the speed and power consequences of process scaling. Presented is a fresh investigation of significantly reducing the power-delay product by lowering the supply voltage to sub-threshold levels. It is shown that a 100-fold energy decrease does not require the added non-recurring engineering costs of scaling down to a smaller CMOS process.

# TABLE OF CONTENTS

| Page                                           |

|------------------------------------------------|

| ACKNOWLEDGEMENTS iii                           |

| ABSTRACT iv                                    |

| LIST OF TABLES viii                            |

| LIST OF FIGURES ix                             |

| CHAPTER                                        |

| 1. INTRODUCTION                                |

| 1.1 Theory of Operation                        |

| 1.2 Design Challenges5                         |

| 2. THE SYSTEM LEVEL                            |

| 2.1 Phase-to-Sine Amplitude Conversion11       |

| 2.2 An Improved Parabolic Sine Approximation17 |

| 2.3 Hardware Complexity Comparison             |

| 3. THE COMPONENT LEVEL                         |

| 3.1 Multiply-Accumulate Circuit                |

| 3.2 Adder Architectures                        |

| 3.3 The Phase Accumulator                      |

| 3.4 Other Design Considerations                |

| 4. THE CIRCUIT LEVEL                           |

| 4.1 Implementation53                           |

| 4.2 Test Procedure                             |

|    | 4.3 Ultra-Low Power/Energy Design | .66 |

|----|-----------------------------------|-----|

| 5. | CONCLUSIONS                       | .80 |

| 6. | BIBLIOGRAPHY                      | .83 |

# LIST OF TABLES

| 2.1. | Comparison of several ROM-based sine approximations                                        |

|------|--------------------------------------------------------------------------------------------|

| 2.2. | Coefficients for a 16-segment parabolic approximation                                      |

| 2.3. | Comparison of SFDR, ROM size, and cost for several recent sine approximations28            |

| 2.4. | Comparison of hardware complexity for recent sine approximations                           |

| 3.1. | Area-delay product for 16-bit parallel-prefix adders                                       |

| 3.2. | Gate and layer count for various serial and parallel-prefix adder architectures            |

| 4.1. | Characteristics of present and future CMOS processes                                       |

| 4.2. | Specifications of CMOS processes to be used in simulations                                 |

| 4.3. | Simulation results of the four types of logic gates for all three CMOS processes           |

| 4.4. | Improvement of gate performance with respect to process                                    |

| 4.5. | Simulation results of the two types of ring oscillators for the three CMOS processes using |

|      | the selected sub-threshold supply voltages71                                               |

| 4.6. | Simulation results of the four logic gates for all three CMOS processes, using sub-        |

|      | threshold supply voltages72                                                                |

| 4.7. | Improvement of gate performance with respect to gate type73                                |

| 4.8. | Overall PDP improvement over the normal $V_{DD}$ 0.25 $\mu m$ gates                        |

| 4.9. | Improvement of the PDP for low-voltage gates                                               |

# LIST OF FIGURES

| 1.1  | Block diagram of a DDFS2                                                                    |

|------|---------------------------------------------------------------------------------------------|

| 1.2  | Output of phase accumulator                                                                 |

| 1.3  | Effect of FCW values on output sine wave                                                    |

| 1.4  | Frequency-domain representation of a channel7                                               |

| 2.1  | Block diagram of phase-to-sine approximation utilizing quarter-wave symmetry12              |

| 2.2  | Block diagram of 1 <sup>st</sup> -order parabolic approximation circuit                     |

| 2.3  | Approximating a sine curve with linear segments                                             |

| 2.4  | Hardware implementation of a segmented linear approximation circuit                         |

| 2.5  | A 2-segment linear approximation                                                            |

| 2.6  | Comparison of approximation errors for a 2-segment approximation                            |

| 2.7  | A 16-segment parabolic approximation                                                        |

| 2.8  | Maximum approximation errors of a 16-segment parabolic approximation and a closer view      |

|      | of the parabolic approximation error                                                        |

| 2.9  | Frequency-domain analysis of a 16-segment parabolic approximation25                         |

| 2.10 | Hardware implementation of a 16-segment parabolic approximation circuit27                   |

| 3.1  | The $8 \times 10 + 12$ multiply-accumulate circuit                                          |

| 3.2  | Architecture of a ripple carry adder                                                        |

| 3.3  | Prefix diagrams for three parallel-prefix adder architectures                               |

| 3.4  | Example of the critical path of a Kogge-Stone adder with high-speed delivery of the upper 4 |

|      | bits40                                                                                      |

| 3.5  | Configuration of a parallel-pipelined phase accumulator                                     |

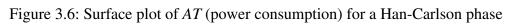

| 3.6 | Surface plot of AT for a Han-Carlson phase accumulator with $\varphi = 4$ , $\gamma = 2$ 45               |

|-----|-----------------------------------------------------------------------------------------------------------|

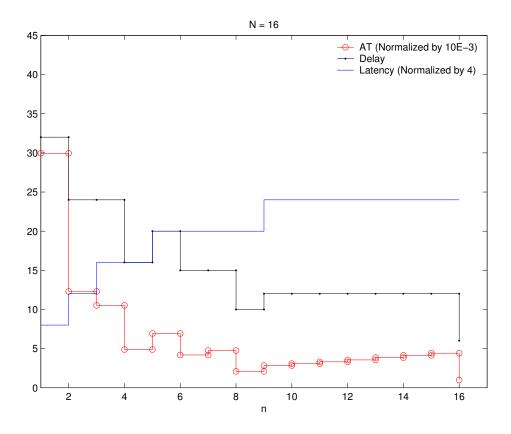

| 3.7 | Superimposed cross section views of AT, delay, and latency for a 16-bit Han-Carlson phase                 |

|     | accumulator with $\varphi = 4$ , $\gamma = 2$ 46                                                          |

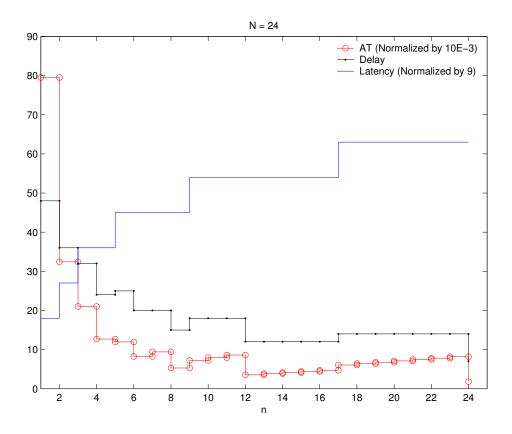

| 3.8 | Superimposed cross section views of AT, delay, and latency for a 24-bit Han-Carlson phase                 |

|     | accumulator with $\varphi = 4$ , $\gamma = 2$                                                             |

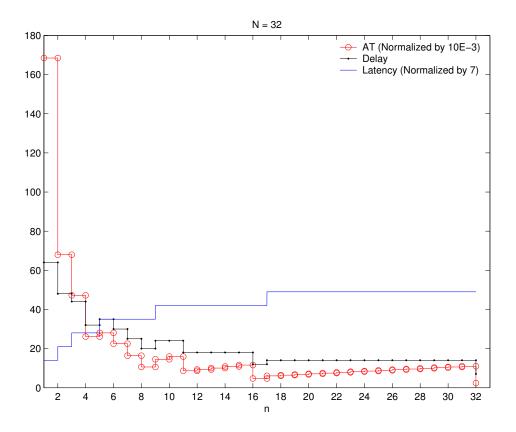

| 3.9 | Superimposed cross section views of AT, delay, and latency for a 32-bit Han-Carlson phase                 |

|     | accumulator with $\varphi = 4$ , $\gamma = 2$                                                             |

| 4.1 | A complementary logic (CMOS) implementation of G54                                                        |

| 4.2 | A pseudo-NMOS logic implementation of G55                                                                 |

| 4.3 | A dynamic logic implementation of G and the clock driver                                                  |

| 4.4 | An implementation of G using differential cascode voltage switch pass gate (DCVS-PG)                      |

|     | logic                                                                                                     |

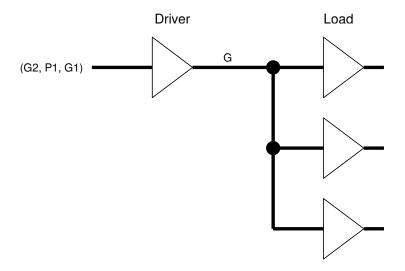

| 4.5 | Driver gate with a fan-out of 3                                                                           |

| 4.6 | A five-node ring oscillator                                                                               |

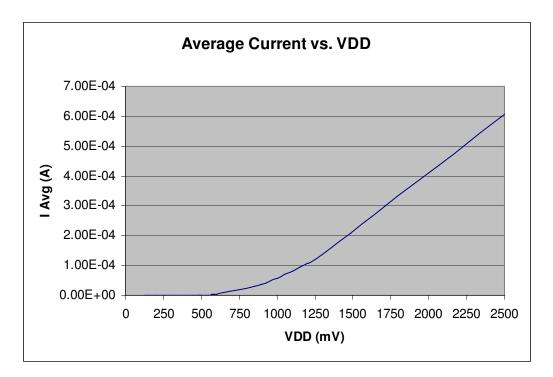

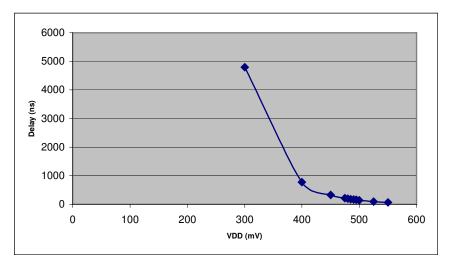

| 4.7 | Plots of the current and delay of a 0.25 $\mu$ m ring-oscillator for several values of V <sub>DD</sub> 69 |

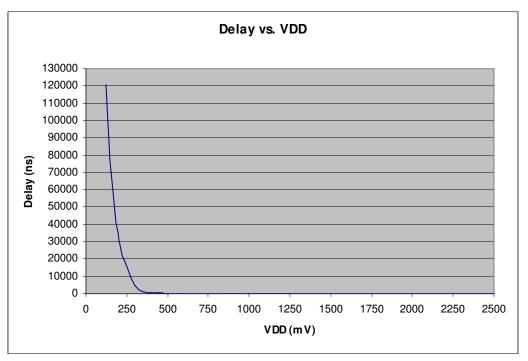

| 4.8 | Closer view of the current and delay plots for a 0.25 $\mu$ m ring oscillator70                           |

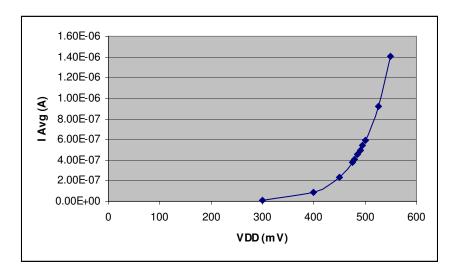

| 4.9 | Comparison of the PDP of a low-voltage gate to its normal $V_{DD}$ counterpart77                          |

|     |                                                                                                           |

#### Dedication

Being the very first graduate of the new Master of Science in Computer Engineering degree at Washington State University, I dedicate this thesis to the following Computer Engineering faculty members: Dr. Valeriu Beiu, Dr. Jabulani Nyathi, and Dr. José G. Delgado-Frias. I express my sincere gratitude to all three professors for their support of my research, and extend a very special thanks to Dr. Delgado for creating this new degree and supporting my efforts to be the first graduate. In addition, I cannot even begin to extend enough thanks to the following persons for all of their support during my graduate career at WSU: Mitchell J. Myjak, Jennifer L. Streicher, and Mrs. Marynella and Dr. Cesario Zamora.

# **CHAPTER 1**

# **INTRODUCTION**

A frequency synthesizer is a quintessential component of any communication system. The fundamental component of an analog or digital communication system is a modulator, which multiplies a base signal containing the data by a carrier frequency that is generated by the frequency synthesizer. While many venerable communication systems, such as AM/FM and VHF/UHF broadcasting, utilize a carrier with a fixed amplitude and frequency, several modern systems utilize spread-spectrum modulation, where the frequency of the carrier varies several times per second [1]. Some well-known spread-spectrum based systems include code division and time-division multiple access (CDMA/TDMA) for cellular communications, direct-sequence spread-spectrum (DSSS) used in IEEE 802.11b wireless Ethernet [2], and frequency-hopping spread spectrum (FHSS) used in Bluetooth<sup>®</sup> [3]. The traditional method of implementing a frequency synthesizer is to use an analog phase-locked loop (PLL), a closed loop system that generates an output frequency based on a fixed reference frequency and a frequency division factor [4]. Because of the inherent closed-loop nature, PLLs have a low frequency switching speed, high phase noise, and stability issues, unacceptable to future generations of highfrequency spread spectrum technologies.

An alternative method of frequency generation is direct frequency synthesis (DFS), which takes a reference frequency and achieves the target frequency through feed-forward analog and digital signal processing techniques, such as filtering and mixing. An improvement of the DFS, and promising alternative to PLLs, is the mostly-digital Direct Digital Frequency

1

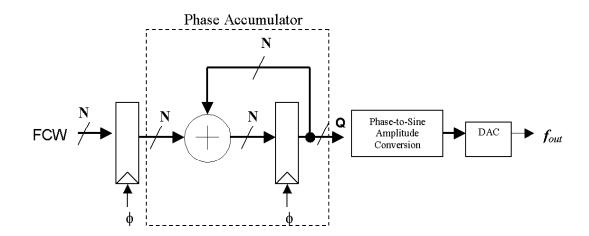

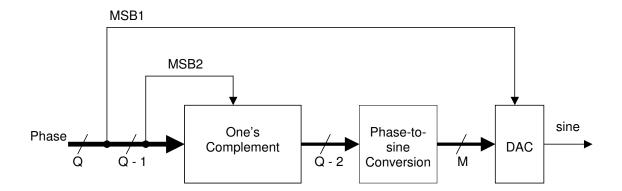

Synthesizer (DDFS) [5][6]. The basic block diagram of a DDFS is shown in Figure 1.1. The essential components are a phase accumulator (PA) with resolution of N bits [7], a phase-to-sine amplitude converter having a resolution of Q (less than N) [8], an M-bit digital-to-analog converter, and normally a low pass filter (not shown). Typically, an M-bit register is placed right before the DAC to pipeline the system and improve the clock frequency. The input to the system is a digital frequency control word, FCW, of length N, leading to an output frequency of:

$$f_{out} = FCW \times f_{clk}/2^N \tag{1.1}$$

According to 1.1,  $f_{out}$  ranges from 0 Hz to a maximum of  $f_{clk}/4$  Hz. Within that range,  $f_{out}$  increases in increments of the frequency resolution,  $f_{clk}/2^N$ . The frequency switching speed is the delay between a change in FCW and the resultant change in  $f_{out}$ . In a non-pipelined system,  $1/f_{clk}$  is the switching speed. For a pipelined system, the switching speed is the total system latency (number of pipeline stages times the clock period).

Figure 1.1: Block diagram of a DDFS.

# **1.1 Theory of Operation**

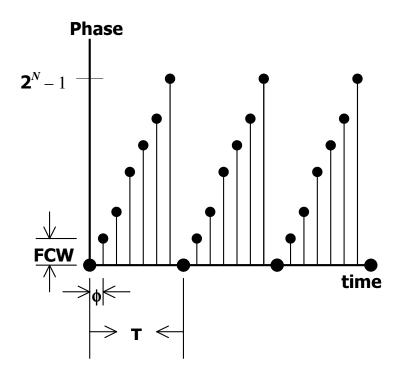

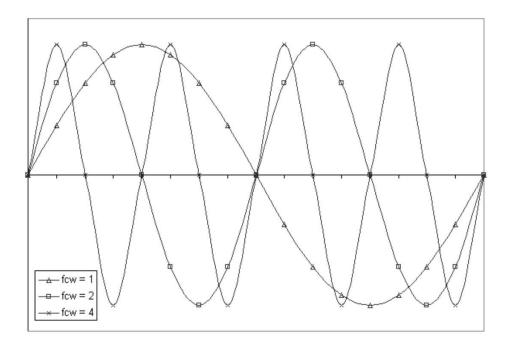

The phase accumulator is a variable-increment N-bit counter. As shown in Figure 1.2, the output increases by *FCW* for every successive clock pulse,  $\phi = 1/f_{clk}$ . When *Phase* >  $2^N - 1$ , the counter overflows and resets to 0. *T* is the duration of one period of the sine curve. For larger values of *FCW* the phase increases at a faster rate, hence a higher frequency wave will be generated, as shown in Figure 1.3.

The phase-to-sine amplitude conversion circuit reads the current value of the phase and outputs the corresponding amplitude for that particular point. The DAC and LPF are optional and used only if an analog output wave is desired.

Figure 1.2: Output of phase accumulator.

Figure 1.3: Effect of FCW values on output sine wave.

# **1.2 Design Challenges**

There exist three primary performance metrics to characterize a DDFS

- 1. Accuracy

- 2. Power Consumption

- 3. Clock Frequency

The accuracy is measured in terms of both the spurious free dynamic range (SFDR) and the maximum approximation error. The maximum approximation error, MAE, is a time-domain metric, and is the difference between an ideal sine wave and the actual DDFS output wave. A smaller MAE is desired. The SFDR is a frequency-domain metric and is the difference between the magnitude of the largest fundamental and the magnitude of the spurious signal (or second largest fundamental). The SFDR (in dBc) is expressed as:

$$SFDR = 20 \log_{10}(A_d/A_s)$$

(1.2)

where  $A_d$  is the amplitude of the first fundamental and  $A_s$  is the amplitude of the second fundamental. A high value of the SFDR is desired. Increasing the precision of N, Q, and Mimprove both the MAE and SFDR.

The clock frequency,  $f_{clk}$ , is the inverse of the maximum propagation delay through the DDFS, determining the maximum attainable output frequency. When a pipelined system is used,  $f_{clk}$  is the maximum propagation delay between two pipeline registers.

The power consumption (in Watts) is the total current that flows between the high and low potential voltage sources times the voltage difference between those two sources. While a low wattage is desired, the power consumption only provides a measurement of the total power used at one single instant. The proper measurement of the total power consumption over an interval is energy, also known as the power-delay product (PDP), and is calculated (in Joules) as:

$$PDP = \text{Total Power Consumption} \times (1/f_{clk})$$

(1.3)

The PDP determines the power supply requirements (i.e. battery life) and the total heat dissipation of the device.

Ideally, a DDFS would achieve optimal values for all three metrics, but realistically only a maximum of two metrics may excel. To increase the accuracy, higher precisions of *N*, *Q*, and *M* are required, increasing the hardware complexity of the phase accumulator, the phase-to-sine amplitude conversion circuit, and the DAC, resulting in increased power consumption, and a slower clock frequency. Using high-speed optimization techniques, such as pipelining [7], a high clock frequency is attainable while maintaining high accuracy, but at a cost of higher power consumption due to the increased circuit complexity from implementing a pipelined system. Conversely, if low-power design techniques are utilized for a high accuracy system, then an optimal speed may not be achieved. Low-power and high-frequency operation are possible, but require low-precision arithmetic components, sacrificing the accuracy.

Because only two optimal characteristic metrics may be achieved, it becomes extremely important to fully understand the requirements of the target application for the DDFS. At the time or printing, the most popular applications of a DDFS are expected to be portable wireless and satellite communications, specifically cellular phones and portable wireless internet-enabled devices, which require a DDFS with high accuracy and low power consumption.

High accuracy is desired to achieve the most efficient use of allocated bandwidth in a finite and crowded wireless spectrum. When transmitting or receiving, each device occupies one

6

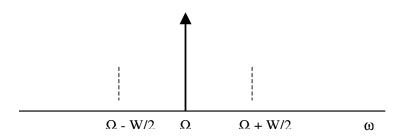

or more channels within the allocated spectrum; the frequency-domain location of that channel is defined by its carrier, or center frequency,  $\Omega$ , and bandwidth, W, as shown in Figure 1.4. Depending on the modulation/multiplexing technologies utilized, each portable device either has distinct ownership of a channel for the entire duration of the transmit/receive session, or changes channels several times per second in a TX/RX session [1]. To allow the maximum number of users, more channels must be fit into the allocated spectrum, further complicated by the requirement for increased channel bandwidth due to increased data transmission rate requirements. As the channels are spaced closer together, the potential for overlapping increases dramatically, which may result in interference and data errors. The error tolerance for the center frequency becomes lower, requiring a highly accurate synthesis of the carrier frequency.

Figure 1.4: Frequency-domain representation of a channel.

Low power consumption is a highly important requirement, simply due to the inherent portable nature of these next-generation wireless devices. Consumers continue to demand cellular phones and wireless internet devices with a smaller footprint, yet with an increased duration of operation (aka "talk time"). Smaller footprints demand smaller batteries with reduced energy capacity. Recent developments in space satellite technology are yielding nanosatellites, which must offer the same high-speed data transmission rates as their larger counterparts, but have much smaller power supplies [9][10]. Batteries in portable devices may even be eliminated with micro-electrical-mechanical systems, MEMS, that generate microwatts of power from waste heat or vibrations. With reduced-capacity power supplies in the future generations of wireless devices, increased duration of operation is only possible if the electronics consume less power than today's devices. Furthermore, as more transistors are accommodated into a single die/package, heat dissipation increases. Unless consumers are willing to accept large heat sinks and/or noisy cooling fans on their portable electronics, low-power operation is mandatory.

Another explosively growing target application suited for a DDFS is remote sensing. Current embedded network sensors are based upon a low-power 4 to 8-bit microcontroller/microprocessor with networking capability, and are intended to be placed in many electronic and non-electronic devices to gather data and transmit it to a central or distributed computing system for analysis [11][12]. The majority of these sensors cannot be placed in a fixed location, and therefore, require some type of wireless data link to the central system. For instance, "smart dust" sensors placed in the air, water, and soil provide precise realtime environmental monitoring. The somewhat controversial radio frequency identification tags, RFID [13], are becoming immensely popular in product warehouses and retail for improved product tracking and inventory management, but were also used most recently at the 2004 Athens Olympic Games for precise timekeeping in the track-and-field events [14]. All of these devices require highly accurate wireless data transmission, although slow data transmission rates are tolerable. Ultra-low power operation is a definite requirement as these devices operate from a very small battery or even lack a battery. For instance, power for RFID tags is generated from induction [15], created by the magnetic field emitted by the tag scanner.

8

#### **Design Objective**

Based on the aforementioned applications for a DDFS, it is obvious that the two major objectives in designing a DDFS to be used for today's popular applications are high accuracy and low power consumption. With the explosive proliferation of ultra-low power sensors, power consumption is expected to be the most important factor. Since the design of a DDFS is very complex, the DDFS must be analyzed and optimized at three levels of abstraction: system, component, and circuit. At the system level, the precisions of the phase accumulator and approximation circuits are determined, as well as the method for approximating the sine wave, and the high-level interconnection topology for the approximation circuit. Analysis at the component level involves selecting the proper architectures of the arithmetic building blocks, and determining if pipelining is appropriate to the DDFS system. At the circuit level, the logic gates are constructed and simulated at the schematic/layout levels. The optimal accuracy and power consumption are obtained by implementing the optimizations from all three levels.

An actual DDFS implementation will not be constructed, as utilizing all of the mentioned optimizations is significantly expensive. If the DDFS is implemented on a full-custom IC, all three abstraction levels may be optimized. However, if the DDFS is implemented on an FPGA or reconfigurable device, optimizations may only take place at the system and component levels. It should be noted that the system and circuit level optimizations presented are not limited to a DDFS system, and may be used in any type of digital IC if its application requirements are similar to those of the DDFS.

9

# **CHAPTER 2**

# THE SYSTEM LEVEL

Analyzing the DDFS at the system level, the required number and precision of the components is determined such that bit widths are minimal but allow the desired frequency resolution and SFDR. At this high of a level, there exists no single number to measure the power consumption or speed, but these metrics are relative to the number of required arithmetic and logic components and their precision, and the size of the ROM (in bits), if required. Fewer and less precise components and a smaller ROM indicate lower power consumption and potentially higher speed. The SFDR and MAE will be determined using Matlab<sup>®</sup> simulations.

#### **Phase Accumulator**

When accuracy is a top-priority, the precision of the phase accumulator is easily determined by solving for N based on the desired frequency resolution.

$$N = \log_{10}(f_{clk} / resolution) / \log_{10}(2)$$

(2.1)

In most circumstances, however,  $f_{clk}$  is not known until testing of the physical DDFS IC. It is imperative that N remains larger than Q, so N is usually set at 16, 24, or 32-bits. 32-bit resolution is most desired for modern applications.

### 2.1 Phase-to-Sine Amplitude Conversion

The accuracy and power consumption are directly influenced by the method of phase-tosine amplitude conversion, as these circuits tend to occupy the majority of on-chip area. The output precision M should be no greater than the precision of the DAC, as any extra bits will simply be discarded. Traditionally, the approximation circuit has been implemented with a fullsize ROM lookup table [5], with the size of the ROM defined as

ROM Size (bits) =

$$M \times 2^Q$$

(2.2)

where M is the output precision and consequently the width of the ROM data bus. Q, the input precision and width of the address bus, is a function of the target SFDR, such that [16]:

$$SFDR \approx 6.02Q - 3.92 \tag{2.3}$$

For example, to achieve a moderate SFDR of 60 dBc, Q = 11, and if M = 12, the lookup table size is 24,756 bits. Assuming that four transistors are required to realize each bit, then over 99,000 transistors are required!

One effective method of reducing the ROM size is to exploit the quarter-wave symmetry properties of the sine curve [17]. As shown in Figure 2.1, the approximation circuits need only generate one quarter of the sine wave, and MSB1 and MSB2 are used as sign bits to mirror the sine curve horizontally and vertically, respectively. This method produces a four-fold decrease in the ROM size.

Figure 2.1: Block diagram of phase-to-sine approximation utilizing quarter-wave symmetry.

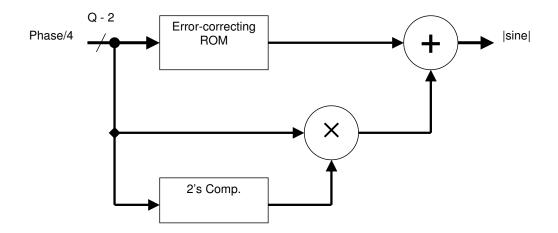

Table 2.1 presents a few ROM-based solutions that use differing techniques to reduce the ROM size. Of particular interest is the first-order parabolic approximation [18]. This method generates a first-order parabola that fits the sine curve using the circuit shown in Figure 2.2. The circuit uses a small error-correction ROM table and a multiplier and adder. The reduced circuit complexity, though, sacrifices the accuracy, as the SFDR is 28.7 dBc, relatively low for today's applications.

| Approximation Method       | Year | MAE     | SFDR (dBc) |

|----------------------------|------|---------|------------|

| Sine-phase difference [19] | 1988 | 0.21125 | 19.06      |

| Double trigonometric [20]  | 1998 | 0.11723 | 27.91      |

| First-order parabolic [18] | 2000 | 0.05600 | 28.68      |

| Piece-wise 3-segment [21]  | 2001 | 0.05500 | 37.49      |

| Meitzler/Millard [22]      | 2003 | N/A     | 83         |

Table 2.1: Comparison of several ROM-based sine approximations.

Figure 2.2: Block diagram of 1<sup>st</sup>-order parabolic approximation circuit.

Figure 2.3: Approximating a sine curve with linear segments.

Several recent approximation methods have significantly reduced the ROM size while providing highly accurate results. These solutions use segmented linear interpolation [23], as illustrated in Figure 2.3. The *x*-axis is divided into *S* equal segments (x1 - x0, ... x16 - x15), and a trendline in the form of  $m_ix + c_i$  is used to 'best fit' the sine curve for each segment. Each segment, denoted by the subscript *i*, has its own unique slope,  $m_i$ , and y-intercept,  $c_i$ . Based on these characteristics, the hardware implementation requires two ROM-lookup tables to store  $m_i$  and  $c_i$ , a multiplier to realize  $m_i x$ , and an adder. Such a circuit, however, is no less complex than any of the previous ROM-based solutions, therefore, special methods have been taken to reduce the complexity. First, because each segment only requires one value of  $c_i$ , the ROM may be implemented with an *S*-to-1 multiplexer (of up to *M*-bits wide), where the individual data pins are tied to logic 1 or 0 to realize  $c_i$ ; the control bus requires  $\log_2 S$  bits. Secondly, *m* is constrained to the interval of [-1, 1] and, may be approximated as the sum of *P* inverse powers-of-two (where  $P = \log_2 S$ ) as shown in 2.4, and therefore,  $m_i x$  may be expressed by 2.5.

$$m_i = \sum_{j=0}^{P-1} m_{ij}, \ m_{ij} \in \{-2^0, -2^{-1}, -2^{-2}, \dots, 0, \dots, 2^{-2}, 2^{-1}, 2^0\}$$

(2.4)

$$m_i x = \sum_{j=0}^{P-1} x m_{ij}$$

(2.5)

Since *x* is multiplied by a single power-of-two, the operation is implemented by shifting *x* to the right by  $-\log_2 |m_{ij}|$  places, and inverting the result if  $m_{ij}$  is negative. Therefore,  $m_i x$  may be realized by adding *S* shifted operands, consistent with the theory of binary multiplication. A hardware block diagram of the segmented linear approximation is shown in Figure 2.4. Physically realizing  $m_i x$  requires *P* multiplexers with *S* inputs of *D*-bit width, where *D* is usually between 10 – 16 bits. For each input, *x* is shifted and inverted accordingly, as denoted by >>. *x* is actually known as the offset angle,  $(x - x_i)$ , and is the lower Q - 2 - P bits of the phase output. The upper *P* bits are used as the multiplexer control bus, and select the proper  $c_i$  and  $m_j$  for each segment. The adder to combine the slopes and y-intercepts requires *P* + 1 inputs and has an

output precision of M. The only ROM used in this approximation is the c multiplexer, and ranges in size from 224 - 960 bits.

The reported SFDR ranges from 48 dBc (for S = 8), to 72 dBc (for S = 16) [24]. For increasing the SFDR and decreasing the MAE, the number of segments has to be increased. Such an approach was recently detailed in [25], with the SFDR being improved to 84.2 dBc (for S = 32), and 96.2 dBc (for S = 64). Obviously, these segmented linear approximations require more and larger multiplexers as *S* increases, and the complexity of the multiple-input adder approaches that of a multiplier.

Figure 2.4: Hardware implementation of a segmented linear approximation circuit.

#### 2.2 An Improved Parabolic Sine Approximation

The segmented linear approximation provides a high SFDR, but still has a relatively high hardware complexity. While attempting to eliminate the use of a multiplier, the structure of the multiple-input adder is very similar to a multiplier. Furthermore, the multiplexers occupy significant area, and will continue to consume significant area as the segment count increases.

The previously mentioned first-order parabolic is revisited. The SFDR is low since the parabola must approximate the entire quarter-wave. The segmented linear approximation has a high SFDR since a best-fit trendline is computed for each segment, but requires many segments for an accurate sine approximation. The positive aspects of both approximation methods can be combined into an improved segmented parabolic approximation [26]. The *x*-axis is still divided into *S* segments, and opposed to a trendline, a parabolic approximation in the general form of:

$$-x^2 + m_i x + c_i \tag{2.6}$$

is used for each segment. Because a parabola inherently follows a sine curve better than a straight line, fewer segments are required. A methodical procedure, optimized for lowering the Maximum Absolute Error (MAE) has been followed, and is applicable for arbitrary segment counts and arbitrary precision. This procedure involves simulating and observing a segmented linear approximation and determining how to reduce the approximation errors.

Before this process may begin, three design parameters must first be known:

- The input precision, Q 2, which should use the smallest reasonable value. Q = 12 bits has been chosen for the approximation circuit presented here.

- The desired number of segments, *S*, which is a power of two. In an effort to minimize hardware complexity, the solution presented uses 16 segments.

• *M*, the final output precision of the phase-to-sine converter, not including the sign bit. The presented solution assumes that a 12-bit binary DAC with built-in sign inversion is to be used.

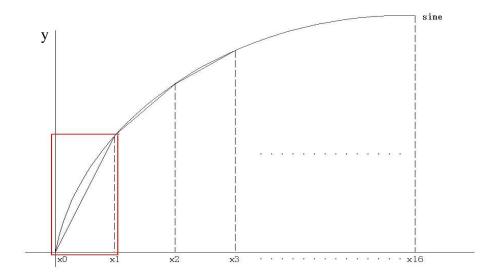

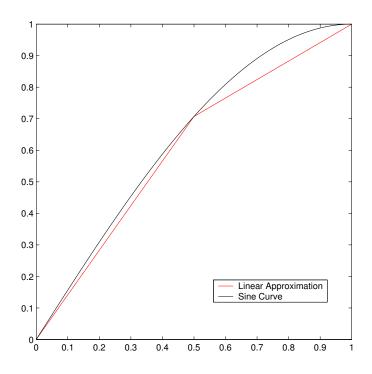

Once the precisions have been obtained, a reference wave with an amplitude precision of M is constructed using Matlab. The *x*-axis is divided into the *S* equal segments, and then  $m_i$  and  $c_i$  are determined for a  $m_i x + c_i$  trendline such that the endpoints lie on the reference wave. The result should be similar to Figure 2.5, which uses only a two-segment example for clarity.

Figure 2.5: A 2-segment linear approximation.

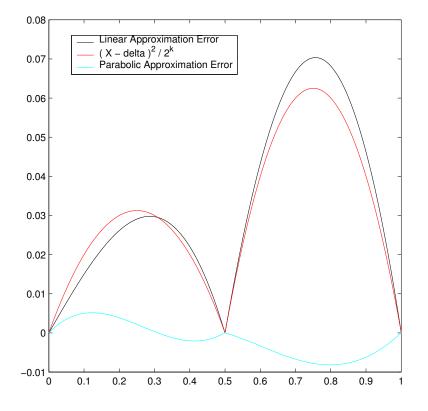

Calculating the difference between the reference wave and the 2-segment linear approximation, it is revealed that the MAE is roughly parabolic in nature, as can be seen in Figure 2.6. This MAE is best approximated with a parabolic correction factor (shown in red on Figure 2.6):

$$-(x - \Delta_i)^2 / 2^{k_i}$$

(2.7)

The parabola is centered in the given segment using  $\Delta_i$ , which has a magnitude of:

$$\Delta_i = 2^{(px-1)}, \tag{2.8}$$

where  $p_x = Q - 2 - \log_2 S$

The division by  $2^{k_i}$  is used to shift the parabola to obtain the best possible fit with the MAE.

Figure 2.6: Comparison of approximation errors for a 2-segment approximation.

The MAE may then be improved by subtracting the parabolic correction factor from the linear approximation, combining 2.7 and 2.9, such that the quantitative description of the approximation is:

$$m_{i}x + c_{i} - (x - \Delta_{i})^{2} / 2^{k_{i}}$$

(2.9)

This equation is expanded to:

$$-x^{2}/2^{k_{-}i} + (2\Delta_{i}/2^{k_{-}i})x - \Delta^{2}/2^{k_{-}i} + m_{i}x + c_{i}$$

(2.10)

Since both the  $m_i$  and  $2\Delta_i/2^{ki}$  coefficients of *x* are constants, they may be added together to form a new (i.e., corrected) slope,  $m_i^*$ . Also  $\Delta_i^2/2^k$  can be added into  $c_i$  to form  $c_i^*$ . The final equation reflecting these modifications is:

$$-x^2/2^{k_i} + m_i^* x + c_i^* \tag{2.11}$$

The MAE of this improved approximation is shown in blue in Figure 2.6 and is much smaller than the MAE of a linear approximation. The SFDR can be calculated by taking the Fast-Fourier Transform of 2.11. Experimenting with Matlab by changing the values of M, Q, and S, and observing the resultant MAE and SFDR allows the optimal precisions to be determined. Note that  $c_i^*$  need only be as precise as M, since additional precision would simply be lost. To increase the magnitude appropriately,  $c_i^*$  can be internally padded with zeros on the least significant end.

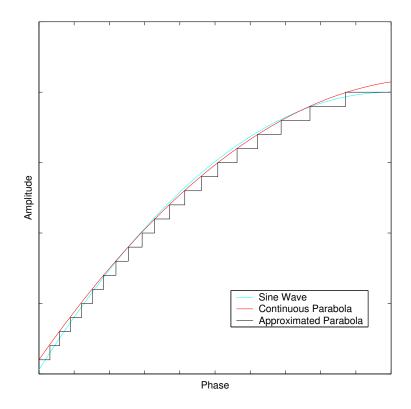

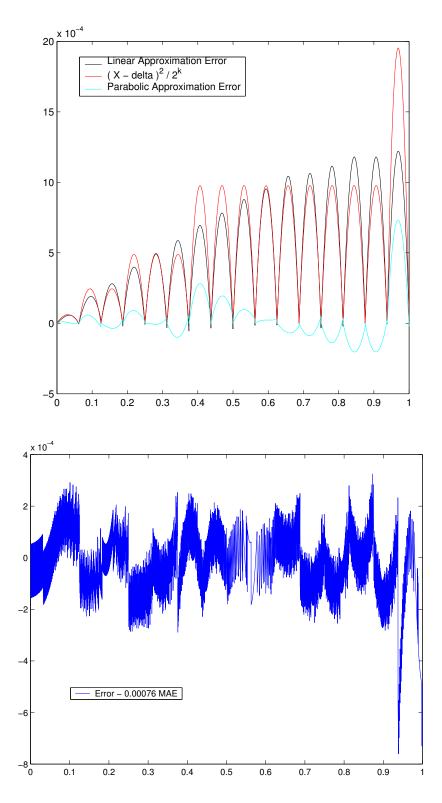

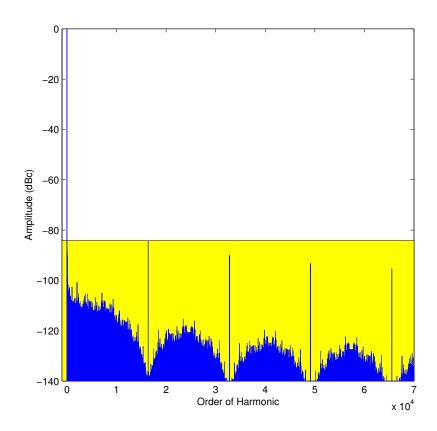

Using the previously stated design parameters: Q = 12, M = 12, and S = 16,  $m_i$ ,  $c_i$ , and  $k_i$ are obtained and detailed in Table 2.2. Figure 2.7 shows a comparison between the reference sine wave and the approximated sine wave for a full 16-segment approximation. The top portion of Figure 2.8 displays the linear approximation error, parabolic correction factor, and paraboliccorrected approximation error. A closer view of the parabolic-corrected approximation error is shown in the bottom portion of Figure 2.8, revealing a maximum approximation error (MAE) of  $7.6 \times 10^{-4}$ . Note that the MAE is largest in the 16th segment, partly due to the fact that the coefficient  $c_{16}$  is slightly altered to keep the output from overflowing (i.e., due to the targeted output precision). An analysis of the final output sine wave in the frequency domain is shown in Figure 2.9. The resultant SFDR is 84.2 dBc, assuming that the DAC causes no profound reduction of the SFDR.

| Segment number, <i>i</i> | $m_i$ | $C_i$ | $k_i$ |

|--------------------------|-------|-------|-------|

| 1                        | 805   | 1     | 7     |

| 2                        | 803   | 403   | 5     |

| 3                        | 788   | 800   | 5     |

| 4                        | 773   | 1190  | 4     |

| 5                        | 743   | 1568  | 4     |

| 6                        | 706   | 1932  | 4     |

| 7                        | 678   | 2276  | 3     |

| 8                        | 628   | 2599  | 3     |

| 9                        | 572   | 2897  | 3     |

| 10                       | 511   | 3167  | 3     |

| 11                       | 445   | 3407  | 3     |

| 12                       | 376   | 3613  | 3     |

| 13                       | 303   | 3785  | 3     |

| 14                       | 227   | 3921  | 3     |

| 15                       | 150   | 4018  | 3     |

| 16                       | 103   | 4074  | 2     |

|                          | l     |       |       |

Table 2.2: Coefficients for a 16-segment parabolic approximation.

\_\_\_\_

Figure 2.7: A 16-segment parabolic approximation.

Figure 2.8: Maximum approximation errors of a 16-segment parabolic approximation (top) and a closer view of the parabolic MAE (bottom).

Figure 2.9: Frequency-domain analysis of a 16-segment parabolic approximation.

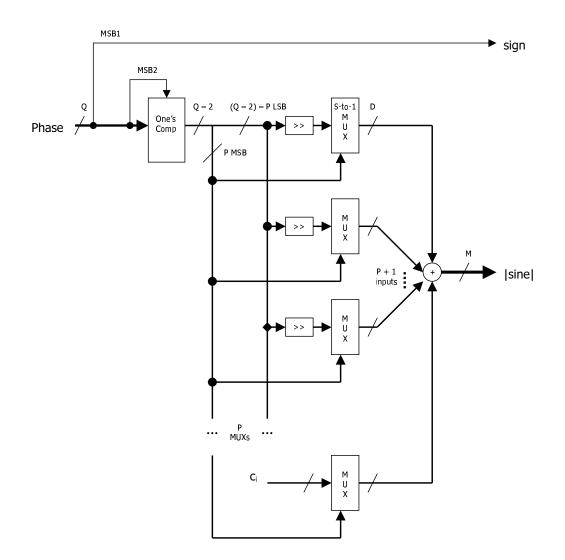

### **Hardware Implementation**

To physically implement this approximation, 2.11 is rewritten as:

$$(m_i^* - x/2^{k_i})x + c_i^* \tag{2.12}$$

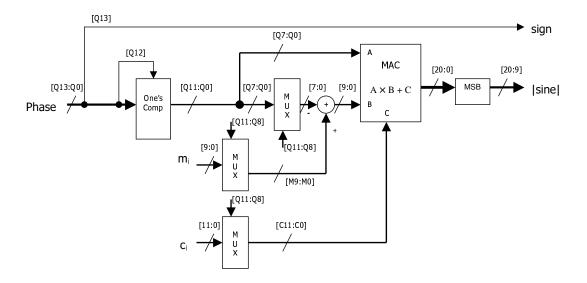

Based on 2.12, this solution requires an adder, a subtractor (adder with one inverting input), and a multiplier. Unlike the segmented linear approximation, x is not being multiplied by a constant, and therefore, the multiplexer/multi-input adder solution cannot be used. An actual multiplier is required, but since the multiplication is followed by an addition operation, a multiply-accumulate circuit (MAC) may be used to streamline operations. Two ROM-lookup tables are required to realize  $m_i^*$  and  $c_i^*$ , but again may be implemented with 16-to-1 multiplexers whose inputs are hard-wired to logic 1 or 0. Dividing *x* (the offset angle) by  $2^{k_i}$  is implemented in the same manner as the segmented linear approximation.  $k_i$  represents the number of rightward shifts of *x* required to fit the parabolic correction factor as close as possible to the linear MAE. Since each segment has its own value of *k*, an additional 16-to-1 MUX is required, with each data input connecting to the shifted *x* for that particular segment. Like the segmented-linear approximation, the multiplexers share a 4-bit control bus, resulting in an 8-bit wide *x*. To minimize the hardware complexity and ROM-size, the smallest possible precisions of the arithmetic components should be used. These precisions are determined by simulating 2.12 in Matlab, adjusting the precisions of *m*, *c*, *k*, and the multiplication and addition/subtraction operations, and observing the effect on the MAE and SFDR.

A hardware block diagram of the approximation using the constants in Table 2.2 and having an 84 dBc SFDR is shown in Figure 2.10. The precisions of all components are listed, with the *m* and *c* ROM having 10 and 12-bit widths, respectively, and the MAC having 8bit  $\times$  10-bit + 12-bit precision. Not shown is the shifting operations between *x* and the MUX, although these do not add to the hardware complexity since *k* is fixed. The final MAC output precision is 21-bits, but only the upper 12-bits are passed on to the DAC. The total ROM size is 400 bits.

Figure 2.10: Hardware implementation of a 16-segment parabolic approximation circuit.

## 2.3 Hardware Complexity Comparison

Table 2.3 displays a comparison of a few most recent methods of sine approximation. The SFDR of the improved 16-segment parabolic is the second highest, and has the second smallest ROM size. To determine which approximations provide a fair compromise between accuracy and circuit complexity, a new measurement is introduced. The Cost is calculated as the ROM size divided by the SFDR. The 16-segment linear approximation offers the lowest cost, although the SFDR is relatively low for today's standards. When a high SFDR is required, then the 16-segment segmented parabolic approximation provides the lowest cost.

| Table 2.3: Comparison of SFDR, ROM | I size, and cost for several recent sine |

|------------------------------------|------------------------------------------|

| approximatio                       | ons.                                     |

| Approximation Mathad   | SFDR  | ROM Size | Cost       |

|------------------------|-------|----------|------------|

| Approximation Method   | (dBc) | (bits)   | (bits/dBc) |

| 16-segment linear [24] | 66    | 224      | 3.39       |

| 32-segment linear [25] | 84    | 448      | 5.33       |

| 64-segment linear [25] | 96    | 960      | 10         |

| Meitzler/Millard [22]  | 83    | 5376     | 64.77      |

| 16-segment parabolic   | 84    | 400      | 4.76       |

The use of the ROM size as a measure of circuit complexity is actually deceiving, as the linear and segmented parabolic approximations, and even the Meitzler/Millard, depend not only on ROM, but on complex arithmetic components, as listed in Table 2.4. Obviously, the segmented parabolic approximation requires a complex MAC and an additional full adder, both

occupying significant area, but theoretically consuming less power than a ROM lookup table of the same physical dimensions. While the linear approximations lack a complex multiplier, the area occupied by a multiple-input adder is similar to a multiplier. Furthermore, the area occupied by the large number of multiplexers required by the linear approximations is significant, and consume nearly the same area as a ROM lookup table. For the 32-segment linear approximation, five *D*-bit 32-to-1 multiplexers are required (where D = 10 - 16), while the segmented parabolic approximation requires only one 8-bit 16-to-1 MUX, one 10-bit 16-to-1 MUX and one 12-bit 16-to-1 MUX.

| Approximation     | Q      | М      | Number of Arithmetic Components |                         |             |

|-------------------|--------|--------|---------------------------------|-------------------------|-------------|

| Method            | (bits) | (bits) | MUX                             | Adders                  | Multipliers |

| Meitzler/Millard  | 12     | 12     | 2 12-bit 2-to-1                 | 2 2-input 12-bit        |             |

| 16-segment Linear | 10     | 11     | 5 <i>D</i> -bit 16-to-1         | 1 5-input <i>D</i> -bit |             |

| 32-segment Linear | 14     | 11     | 6 <i>D</i> -bit 32-to-1         | 1 6-input <i>D</i> -bit |             |

| 64-segment Linear | 16     | 12     | 7 D-bit 64-to-1                 | 1 7-input <i>D</i> -bit |             |

| Segmented         | 12     | 12     | 1 8-bit 16-to-1, 1 10-          | 1 2-input 8-bit & 1     | 1 8×10 bit  |

| Parabolic         |        |        | bit 16-to-1, & 1 12-bit         | 2-input 21-bit          |             |

|                   |        |        | 16-to-1                         |                         |             |

Table 2.4: Comparison of hardware complexity for recent sine approximations.

## **CHAPTER 3**

# THE COMPONENT LEVEL

Once the required number of adders and multipliers and their precision(s) is determined at the system level, the appropriate architectures are selected with regards to the speed (clock frequency) and power requirements. Based on Figures 1.1 and 2.10, the most complex components of the segmented parabolic DDFS system are the multiply-accumulate unit and the phase accumulator. At this level, the arithmetic component architectures are characterized in terms of gates, where a gate denotes a simple or complex logic component that performs an operation fundamental to a multiple bit adder or multiplier, such as XOR or AND/OR. The power consumption is represented by the gate count, where the more gates equals higher power consumption. The speed is estimated by identifying the worst-case path through the adder of multiplier, and is expressed in terms of gate delays (or layers), which is the total number of gates in the worst-case path.

### **3.1 Multiply-Accumulate Circuit**

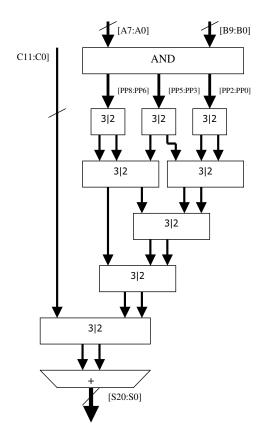

Because of the inherent complexity of a multiplier circuit, the  $8 \times 10 + 12$  MAC poses a very significant speed and power consumption bottleneck. A traditional multiplier uses array multiplication, yet the resultant structure has a long propagation delay and occupies a large area [27]. An alternative solution is to use a Wallace-Tree multiplication structure [28]. Based on the theory of binary multiplication, multiplying an 8-bit operand A by the 10-bit wide B expands to:

|                 |            |            | $PP_{0,9}$ | ••• |            | $PP_{0,0}$       |

|-----------------|------------|------------|------------|-----|------------|------------------|

|                 |            | $PP_{1,9}$ | •••        |     | $PP_{1,0}$ |                  |

|                 |            | <br>       |            |     |            |                  |

| +               | $PP_{7,9}$ | <br>       | $PP_{7,0}$ |     |            |                  |

| Z <sub>20</sub> |            | <br>       |            |     | $Z_1$      | $\overline{Z}_0$ |

where Z denotes the final product, and  $PP_{ij}$  denotes one bit of a partial product, resultant from an AND-ing operation ( $A_0B_0 \dots A_7B_9$ ). This operation is essentially the addition of the eight shifted 10-bit partial products. Since a full adder can process only two operands, the 8 partial products must be reduced using carry-save arithmetic. The reduction is handled by using a series of interconnected binary full adders, heretofore referred to as 3l2 counters, as shown in Figure 3.1. The propagation delay through this multiplier is four 3l2 counter delays plus one AND operation delay. The addition of the 12-bit operand, C, adds one additional layer of 3l2 counters. However, the multiplication-addition result is in carry-save format, where the result is represented by twenty individual Sum and Carry bits. To concatenate these bits into the standard sum format, a 21-bit (20 Sum + 1 Carry) full adder is required.

Figure 3.1: The  $8 \times 10 + 12$  multiply-accumulate circuit

## **3.2 Adder Architectures**

Based on Figures 1.1, 2.10, and 3.1, the most fundamental arithmetic component of the DDFS is the adder. There are two basic types of adders that comprise the design: single-bit operand binary adders and multiple-bit operand full adders. The multiplication of the MAC is performed by a Wallace tree connectivity pattern of 3l2 counters. The truth table of a single 3l2 counter is shown below:

| Α | В | Cin | S | Cout |

|---|---|-----|---|------|

| 0 | 0 | 0   | 0 | 0    |

| 0 | 0 | 1   | 1 | 0    |

| 0 | 1 | 0   | 1 | 0    |

| 0 | 1 | 1   | 0 | 1    |

| 1 | 0 | 0   | 1 | 0    |

| 1 | 0 | 1   | 0 | 1    |

| 1 | 1 | 0   | 0 | 1    |

| 1 | 1 | 1   | 1 | 1    |

Therefore, the logical equations of a 3l2 counter are  $S = A \oplus B \oplus C$  and Cout = AB + BC + AC. The half adder (HA), or 2l2 counter, has logical equations  $S = A \oplus B$  and Cout = AB. Implemented using conventional complementary logic, a 3l2 counter has a minimum delay of two gates.

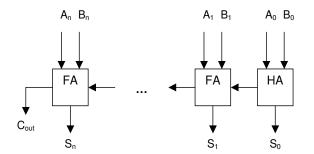

The phase accumulator, MAC, and approximation circuit rely on more complex full adder circuits that process operands of 8 to 32 bits wide. The simplest implementation of a full adder is a ripple carry adder (RCA) [29], shown in Figure 3.2, which is a serial chain of 3l2 counters plus an initial 2l2 counter. Because one 3l2 counter is required for every bit in the addition operation, N - 1 3l2 + 1 2l2 counters are required, resulting in a total delay of 2N gates, and a total gate count of 7N gates, when using simple 2-input AND/OR/XOR gates. Therefore, a 32-bit RCA has a 64-gate delay and gate count of 224 gates. The RCA offers the smallest gate count out of any full adder architecture, but has the longest delay, which is considered very slow, even for low-power applications.

Figure 3.2: Architecture of a ripple carry adder (RCA).

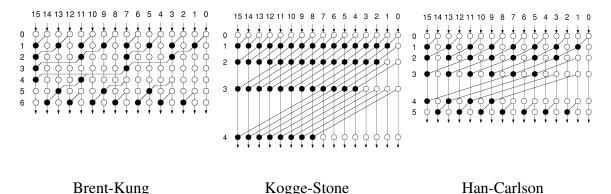

For the DDFS to achieve high-speed operation, the selection of the full adder architecture is usually limited to those with a lookahead structure, otherwise known as parallel-prefix. The highest performance parallel-prefix adders (PPA) are the Brent-Kung, Kogge-Stone, and Han-Carlson architectures [29]. At the component level, the topology of these adders is depitcted by a prefix diagram to clearly indicate the gate count, delay, fan-in, and fan-out. A prefix diagram for a 16-bit Brent-Kung, Kogge-Stone, and Han-Carlson adder is shown in Figure 3.3. Each black circle in the diagram denotes an associative operation, while each white circle is simply a buffer, where the output is the same as the input; the lines represent the path of the signals. A prefix diagram has the dimensions  $N \times m$ , where N is the precision of the adder and m is total number of rows containing at least one black circle. Descending in hierarchy, the associative operations of a black circle are comprised of two logic equations to calculate the propagate and generate signals, such that:

$$P_{i,j} = P_{i-1,j}P_{i-1,j-1}$$

$$G_{i,j} = G_{j-1,j} + P_{j-1,j}G_{j-1,j-1}$$

where *i* is the layer number, and *j* is the bit number. Not shown in the diagrams is a top layer that computes the initial values of P and G, where  $P_j = A_j \oplus B_j$  and  $G_j = A_jB_j$ , and a final layer responsible for calculating the final sum, where  $S_j = P_{0,j} \oplus G_{m-1,j-1}$ .

Figure 3.3: Prefix diagrams for three parallel-prefix adder architectures [29].

Based on the prefix diagrams, the gate count is the number of black circles times the number of gates in each black circle, plus two gates for every bit in the top layer, and one gate for every bit in the final layer. The worst-case delay is obtained by multiplying *m* by the number of gate delays per black circle and adding the delay of the top and final layers. However, to accurately characterize the speed and power consumption of a PPA, it becomes necessary to consider the symbolic Fan-In (FI) and Fan-Out (FO). The FI is the total number of distinct inputs to a black circle, while the FO is the number of subsequent black and white circles driven by that particular circle. FI and FO are a representation of the total input and output parasitics, respectively, of the equivalent logic gates for each circle. As FI or FO increases, the equivalent total load capacitances and resistances increase, hence increasing the actual power consumption and the maximum propagation delay. To decrease the delay when FI or FO is large (usually

greater than 2), higher speed gates may be used, but at the expense of further increasing the power consumption.

Based on the prefix diagrams for a N = 16 adder, the fastest architecture is the Kogge-Stone model, requiring only 6 symbolic delay layers, including the first and last layers not shown in the diagram, and having a 12-gate delay assuming each layer has a 2 gate delay. For any value of *N*, both FI and FO are bounded to a maximum of 2. Of the three architectures, the Kogge-Stone is the most hardware intensive, requiring 49 black circles and, consequently, 146 gates (assuming 1 gate to implement each logic equation). Conversely, the Brent-Kung model provides the lowest hardware complexity requiring only 26 black circles; however, the maximum delay rises to eight symbolic layers. While FI is finitely bounded to 2 for any *N*, FO is logarithmically bounded to  $\log_2 N$ , indicating slower operation and/or a higher power consumption as *N* increases. Compromising between the lowest hardware complexity of the Brent-Kung model and the high-speed and bounded FI and FO of the Kogge-Stone, the Han-Carlson offers seven symbolic delay layers, but requires only 32 black circles.

To assist in selecting an appropriate architecture, an unofficial approximation of the areadelay product (ADP) may be calculated. This function is a rough estimate of the PDP, and is defined as the Gate Count times the Delay. To account for the effects of fan-out, the result is multiplied by 1 for those architectures with a bounded FO of 2. When the fan-out is unbounded, it is assumed that the delay and/or power consumption are affected by at least 2%. Therefore, when the FO is greater than 2, the ADP is multiplied by 1 plus two-percent of the maximum FO. Table 3.1 lists the resultant ADP for 16-bit Kogge-Stone, Brent-Kung, and Han-Carlson adders (a lower value is better). The Kogge-Stone has the highest ADP due to its large hardware complexity. The Brent-Kung has a relatively large ADP as well, somewhat due to the effects of fan-out, but mostly due to the long delay. The Han-Carlson has the lowest ADP thanks to its lower hardware complexity.

| A            | Area-Delay Product   |  |  |

|--------------|----------------------|--|--|

| Architecture | (Gates × Gate Delay) |  |  |

| Kogge-Stone  | 1752                 |  |  |

| Brent-Kung   | 1696                 |  |  |

| Han-Carlson  | 1568                 |  |  |

Table 3.1: Area-Delay Product for 16-bit parallel-prefix adders.

Observation of the prefix diagrams reveals that the delay is  $\log_2 N$  constrained, significantly smaller than a serial adder with a linear or quadratically constrained delay. The gate count, however, is a function of  $N \log_2 N$ , significantly larger than a serial adder. Table 3.2 lists several popular serial and parallel-prefix adders and actual equations expressing the total number of gates and gate delays [29]. The equations of the Han-Carlson adder have unknowns ( $\Gamma$ ,  $\Phi$ ,  $\Delta$ ) since the Han-Carlson is actually a hybrid of the Kogge-Stone and Brent Kung and cannot be reasonably expressed in equations. To simplify the comparison between adder architectures and select an appropriate model based on power and speed requirements, an asymptotic model may be used. Based on the equations in Table 3.2, for a parallel-prefix adder, it is reasonable to assume that the area and delay, *A* and *T*, respectively, for any parallel-prefix adder structure can be represented as:

$$A = \alpha N \log_2 N \tag{3.1}$$

$$T = \beta \log_2 N \tag{3.2}$$

where  $\alpha$  and  $\beta$  are coefficients for the particular type of adder, and may be derived from Table 3.1. For a Han-Carlson adder, it is reasonable to assume that  $\alpha = \frac{1}{2}$ . It should be noted that these asymptotic models are very liberal in their approximations, and may require precise tweaking of  $\alpha$  and  $\beta$ . With *A* and *T*, a more precise area-delay product, *AT*, (corresponding to power consumption) and power delay product, *AT*<sup>2</sup>, (energy) may be calculated.

| Adder                                                 | Number of Gates            | Number of Gate Delays |

|-------------------------------------------------------|----------------------------|-----------------------|

| Ripple Carry                                          | 7 <i>N</i> + 2             | 2 <i>N</i>            |

| Carry-Skip                                            | $8N + 6\sqrt{(N-1)} - 6$   | $4\sqrt{(N-1)}$       |

| Carry-Select                                          | 14N - 5k - 5               | 2 <i>k</i> + 2        |

| $k = \left\lceil 1/2\sqrt{(8N-7)} - 1/2 \right\rceil$ |                            |                       |

| Carry-Increment                                       | 10N - k + 2                | $2.8\sqrt{N}$         |

| $k = \left\lceil 1/2\sqrt{(8N-7)} - 1/2 \right\rceil$ |                            |                       |

| Brent-Kung                                            | $10N - 3 \log_2 N - 1$     | $4 \log_2 N$          |

| Kogge-Stone                                           | $3N\log_2 N + N + 8$       | $2\log_2 N + 4$       |

| Han-Carlson                                           | $\Gamma N \log_2 N + \Phi$ | $2 \log_2 N + \Delta$ |

|                                                       | I                          |                       |

Table 3.2: Gate and layer count for various serial and parallel-prefix adder architectures [29].

#### 3.3 The Phase Accumulator

When having a high clock-frequency is a major consideration, the maximum delay through the phase accumulator poses significant limits. The total PA delay is the adder propagation delay plus the delay of one register.

#### **Improving the Adder**

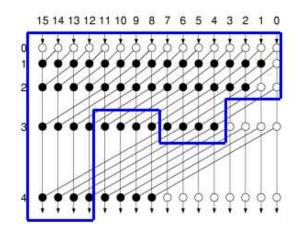

Constructing a parallel-prefix adder minimizes the delay, and is imperative even for lowpower implementations, but power consumption remains high. However, unlike an adder in a general-purpose microprocessor, it happens that only certain portions of the adder must operate at a high speed. The phase-to-sine approximation uses Q = 8 - 16 bits, requiring that these upper sum bits be available as fast as possible. The remaining N - Q sum bits need not be available as quickly, but the upper Q sum bits depend on the carry bits from those lower N - Q bits. Based on this requirement, there exists critical and non-critical paths through the adder. The critical path is identified by viewing the prefix diagrams and tracing the path from the output of those Q bits all the way back to the inputs. Any black circles in the way of the path form the critical path and must operate at a high speed. The black circles not included in the critical path may operate at a slower speed (hence using less power). Figure 3.4 displays an example of an illustration of the critical and non-critical paths for a 16-bit Kogge-Stone where Q = 4. The critical path is comprised of all those black circles within the blue outline. The physical realization of this lower power adder is achieved at the circuit level by constructing the non-critical P, G, and XOR logic gates with transistors smaller than those of the critical gates.

Figure 3.4: Example of the critical path of a Kogge-Stone adder (inside the blue outline) with high-speed delivery of the upper 4 bits.

#### Pipelining

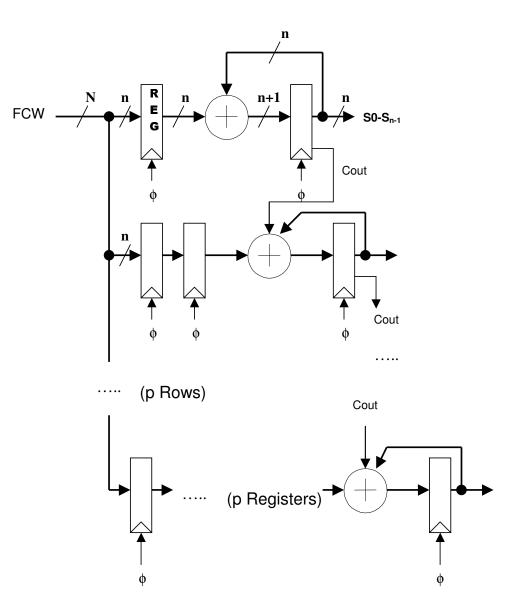

When a smaller PA delay is desired, pipelining may be utilized at the expense of further increased power consumption [7]. As displayed in Figure 3.5, the PA is divided into p pipeline stages of n bits each, such that np = N (or equivalently p = N/n). Each adder outputs n + 1 bits: nsum bits, and one carry output bit. These bits are stored in an end register. The n stored sum bits then feed back into the adder, and the latched carry output bit connects to the carry input of the adder in the next pipeline stage. To store the upper Q = 10 - 12 bits, additional end registers must be placed on the p - 1, p - 2, ... stages of the pipeline. p clock cycles are required to fully initialize or flush the pipeline. While a non-pipelined PA requires only two N-bit register banks, the total number of flip-flops for a multiple stage pipelined PA is obtained based on equation 3.3:

$$FF_{Total} = \frac{p(p+1)n}{2} + p(n+1) + End_{FF} - 1$$

(3.3)

To determine the end register requirements for a Q-bit phase-to-sine conversion circuit assuming Q < N:

$$End\_FF = \begin{cases} Q-n, & \text{if } A = 0 \text{ and } Q-n \ge 0\\ An, & \text{if } A \neq 0 \text{ and } Q-n \ge 0\\ 0, & \text{else} \end{cases}$$

$$A = \sum_{j=0}^{j < \lceil Q/n \rceil} j$$

(3.4)

Figure 3.5: Configuration of a parallel-pipelined phase accumulator.

It follows that a parallel-pipelined PA requires almost twice as many flip-flops as a single-stage pipelined PA. Based on equations 3.1 - 3.4, it is possible to estimate an optimal *n* with respect to minimal power. The total area of the PA can be represented as:

$$A(N, n) = \varphi FF_{Total}(N, n) + \alpha n \log_2 n$$

(3.5)

The latency *L* of one pipeline stage is:

$$L(N, n) = \beta \log_2 n + \gamma \tag{3.6}$$

The total delay through the PA (from the  $1^{st}$  to  $m^{th}$  stage) is:

$$T(N, n) = p L(N, n) \tag{3.7}$$

Here  $\varphi$  and  $\alpha$  are the area coefficients of a flip-flop and gate that comprises the black cell, respectively, and  $\beta$  and  $\gamma$  are the associated delay coefficients. More precisely,  $\varphi$  is the ratio of the power dissipation of a flip-flop to that of an adder gate. Since the actual power dissipation is not known until completion and simulation of the IC layout,  $\varphi$  may be estimated as the ratio of the number of transistors composing a single flip-flop to the number of transistors in a single adder gate. High-speed flip-flops produced with current CMOS processes are composed of 15 – 25 transistors, and a single adder gate consists of 4 – 8 transistors using standard CMOS, pseudo NMOS, dynamic, or static threshold logic [27] – [32]. Consequently, it is estimated that  $\varphi = 2...4$ . In a standard 0.25 µm CMOS process, adder gates with a delay of 50 – 100 ps [30][31], and flip-flops with a delay of 125 – 300 ps [32] have been reported. Therefore, it may be concluded that  $\gamma = 1...6$ .

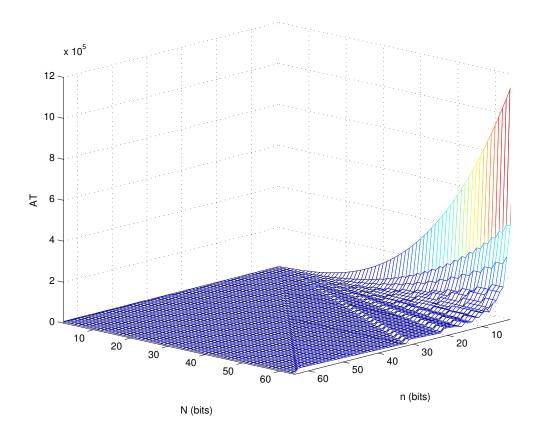

The measures AT and  $AT^2$  will be used for finding optimal designs for the PA. Using equations 3.5 - 3.7, the optimal *n* values can be determined. The simplest method is to create surface plots of *L*, *T*, and *AT* for all practical values of *N* and *n*. For a PA with Q = 12constructed with a Han-Carlson connectivity pattern adder, and with  $\varphi = 4$  and  $\gamma = 2$ , the *AT* surface plot is shown in Fig. 3.6. Interpreting the surface plot, maximizing *n* minimizes power consumption since fewer flip-flops are used in the design. Of course, increasing n also increases the latency.

To determine the optimal *n* for a given *N*, it is useful to take a cross section view of the *AT*, delay, and latency surfaces, and superimpose them on the same plot. Results for N = 16, 24, and 32 are shown in Figures 3.7 - 3.9. Note that the *AT* and latency cross-sections have been normalized in order for all three views to be visible on the same plot. As observed from the three figures, the lowest power consumption occurs at n = N. This result is expected, since the minimum number of flip-flops is used, of course this configuration has the largest latency. If a smaller latency is desired, but within low power consumption limits, all the plots show that n = N/2 is an excellent power-latency combination. The smallest latencies are achieved for n = 1, with the power consumption jumping to nearly 32 times the minimal value!

accumulator with  $\varphi = 4$ ,  $\gamma = 2$ .

Figure 3.7: Superimposed cross section views of AT, delay, and latency

for a 16-bit Han-Carlson phase accumulator with  $\phi = 4$ ,  $\gamma = 2$ .

Figure 3.8: Superimposed cross section views of AT, delay, and latency

for a 24-bit Han-Carlson with  $\phi = 4$ ,  $\gamma = 2$ .

Figure 3.9: Superimposed cross section views of AT, delay, and latency

for a 32-bit Han-Carlson phase accumulator with  $\phi$  = 4,  $\gamma$  = 2.

## 3.4 Other Design Considerations

Pipelining the phase accumulator definitely provides a significant improvement to the overall clock frequency. However, the PA is not the only major speed constraint. Assuming that an *M*-bit register is placed before the DAC (where *M* is the DAC precision), the propagation delay through the phase-to-sine approximation circuit must be equal to or less than the latency of a single PA pipeline stage, otherwise a higher clock frequency cannot be used. Coupled with the fastest parallel-prefix adder, the Kogge-Stone, the minimum delay of the MAC circuit is 18 gates. Assuming a 2-gate delay for each multiplexer, the total approximation circuit delay is at least 25 gates. Therefore, pipelining the approximation circuit is imperative. Because there are no feedback components, pipelining the MAC (and the other components) is relatively trivial. With some minor modifications, the same type of mathematical model used with the PA may be used to determine the optimal number of pipeline stages.

With the introduction of pipelining, questions arise to the issue of data hazards, as in a pipelined microprocessor. Because the DDFS always executes sequentially, there exists no data hazards, and no need to "stall" execution. However, deepening the pipeline increases the total system delay, consequently reducing the frequency switching speed. When the value of FCW changes, p clock cycles (where p = Total Pipeline Stages) are required until the output based on the new FCW is seen at the output of the DAC. Should the target application have a rapidly changing FCW, then a deep pipeline is probably not appropriate.

Like the phase accumulator adder, the 21-bit MAC adder may be modified to reduce power consumption. A critical path exists for those upper 12-bits of the output used by DAC. The black circles that comprise the remaining non-critical path of the lower 9-bits may be completely eliminated, as those bits are not required anywhere else in the circuit.

49

## **CHAPTER 4**

# THE CIRCUIT LEVEL

Observing the DDFS from both the system and component levels, the adder is obviously the most common and largest component of DDFS, since a segmented parabolic implementation requires three 8, 21, and 32-bit adders. Second to the pipeline registers, the adders singlehandedly influence the overall speed and power consumption. Circuit level analysis descends into the black circles of the parallel-prefix adders to design, simulate, and characterize the comprising logic gates. While this section focuses exclusively on those black cell logic functions, the analysis techniques may be applied to any type of CMOS logic gate in a fullcustom IC. To fully understand the motivation behind these techniques, a fundamental understanding of the power consumption of an IC is required

#### **Power Consumption**

The total power consumption (in Watts) of a single logic gate is calculated as:

$$P_{Total} = V_{DD} I_{TOTAL} \tag{4.1}$$

where  $I_{TOTAL}$  is the total current that flows between  $V_{DD}$  and GND. P<sub>Total</sub> can also be expressed as:

$$P_{Total} = P_{Static} + P_{Dynamic} + P_{Leakage}$$

$$\tag{4.2}$$

$P_{Static}$  is the power dissipated when there exists one or more short-circuit or low-

impedance paths between  $V_{DD}$  and GND. There is no standard equation for  $P_{Static}$  as it is based on the number of short-circuit paths, their respective impedances, and the duration for which there exists a short-circuit. The impedance is a function of the width of the transistor(s) that form the short-circuit path(s), where wider transistors have lower impedance.

$P_{Dynamic}$ , which is the power dissipated during  $0 \rightarrow 1$  or  $1 \rightarrow 0$  transitions due to the charging and discharging of load and parasitic capacitances through parasitic resistances, is calculated as

$$P_{Dynamic} = C_L V_{DD}^2 f \alpha \tag{4.3}$$

where  $C_L$  is the total equivalent load and parasitic capacitance, proportional to the on-chip area, f is the operating frequency (the clock frequency in a pipelined system), and  $\alpha$  is the switching activity factor.  $f \propto RC_L$ , where R is the sum of the interconnect and drain-source resistances between  $C_L$  and  $V_{DD}$  or GND. When  $\alpha = 1$ , every transistor in a gate switches during every  $0 \rightarrow 1$  or  $1 \rightarrow 0$  transition. Realistically, such an occurrence is very uncommon, and usually  $\alpha = 10\%$ .

$P_{Leakage}$  is the power dissipated when current flows between the drain and source of a MOSFET while it is operating in the cutoff region. The leakage current for a gate is calculated as:

$$I_{Leakage} = W_{eff} I_s e^{\frac{V_{TH}}{V_o}}$$

(4.4)

where  $W_{eff}$  is the effective width of the cell,  $I_s$  is the effective zero-threshold leakage current, and  $V_o$  is the sub-threshold slope [33].

The power delay product,  $P_{Total} \times (1 / f)$ , determines the total energy usage, directly related to the battery life and the heat dissipation. The objective is to minimize either  $P_{Total}$  or *Delay*, but realistically only  $P_{Total}$  is minimized due to the linear relationship between *Delay* and  $P_{Dynamic}$ .

In order to reduce  $P_{Total}$ , one or more of the three components must be decreased.  $P_{Static}$  is minimized by reducing the number of short-circuit paths and increasing the impedance of those paths that cannot be eliminated. Decreasing *f* linearly decreases  $P_{Dynamic}$ , but this option is not usually possible when maximum speed operation is always desired. A more realistic method is to decrease  $C_L$ , by minimizing the hardware complexity and interconnect lengths, and also by minimizing transistor widths (but at the possibility of decreasing *f*). Decreasing  $V_{DD}$  causes a quadratic decrease, at the expense of reduced noise margins and the possibility of incorrect outputs.

## **4.1 Implementation**

For a parallel-prefix adder, the two separate logical functions represented by a black cell with a symbolic fan-in of 2 are [29]:

$$P = P_n P_{n-1}$$

$$G = G_n + P_n G_{n-1}$$

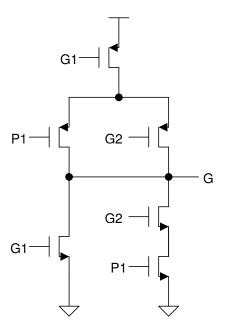

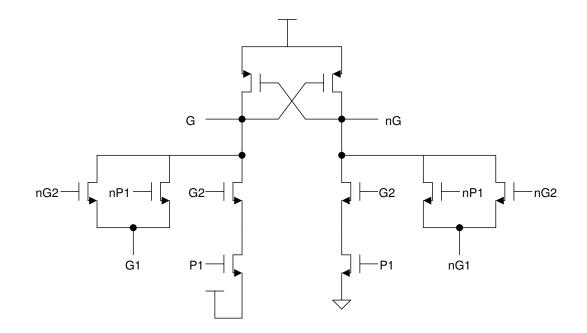

P is implemented with a two-input NAND gate. Using discrete logic gates, G requires two NAND gates, experiencing a delay at least twice as long as P. To conserve both area and speed, G may be implemented with a single complex logic gate where the delay, although larger than P, will be smaller than using two discrete gates. Because G is inherently the slower and greater power consumer of the two functions, the design and testing process presented is exclusively for an implementation of G, but can be applied to any type of logic gate. There exist four popular Boolean logic styles for implementing G in a CMOS process.

The most traditional implementation uses complementary logic, or hereafter referred to as CMOS [27], shown in Figure 4.1. G (or rather the inverse) is realized using the NMOS pulldown network, and the complementary PMOS pull-up network provides the logic 1 output. Based on the logic structure, there cannot exist a constant short-circuit or low-impedance path between  $V_{DD}$  and GND, eliminating  $P_{Static}$ . Due to the complementary network, any input transition must switch at least two transistors, such that the driver gate sees a large input capacitance. Additionally, having complementary transistors increases the total output load capacitance,  $C_L$ , resulting in a large  $P_{Dynamic}$ , and increases the series resistance for charging or discharging the load capacitance, thereby decreasing the speed. Except in rare circumstances, the output voltage for logic 1 always swings to  $V_{DD}$ , and GND for logic 0.

53

Figure 4.1: A complementary logic (CMOS) implementation of G.

Figure 4.2 shows a pseudo-NMOS implementation of G, where the complementary pullup network has been replaced by a single always-on PMOS transistor [27]. The width of this transistor is normally smaller than the equivalent width of the CMOS pull-up network, reducing  $C_L$ , the total input capacitance, and the series resistance. Because this transistor is always on, however, there exists a low impedance path between  $V_{DD}$  and GND during logic 0 outputs. This situation poses two major challenges. First,  $P_{Static}$  is large, and when averaged, dominates  $P_{Total}$ . Second, the noise margins are smaller than a CMOS gate. For a logic 1 output, G swings to  $V_{DD}$ , but during a logic 0, G does not swing to GND, but:

$$V_{out} = V_{DD} \left[ R_N / (R_N + R_P) \right]$$

(4.6)

where  $R_N$  and  $R_P$  are the equivalent series resistances of the NMOS and PMOS transistors, respectively. If  $V_{out}$  is greater than 10% of  $V_{DD}$ , the transistors in the load devices connected to the output may instead recognize a logic 1 output. To keep  $V_{out}$  below 10% of  $V_{DD}$ , the widths of the PMOS and NMOS transistors should be reduced, and while  $P_{Static}$  is reduced, the speed is reduced.

Figure 4.2: A pseudo-NMOS logic implementation of G.

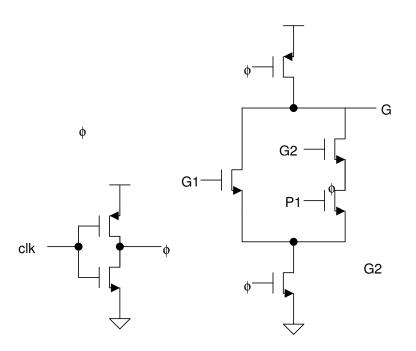

Shown in Figure 4.3 is a dynamic logic gate, and an inverter used in the clock distribution network [27]. The pull-down network is connected to  $V_{DD}$  and GND by a PMOS and NMOS transistor, respectively, whose gates are connected to a common clock,  $\phi$ . The configuration of this gate results in two phases of operation, pre-charge and evaluate. During pre-charge,  $\phi$  is at logic 0, turning on the PMOS and turning off the lower NMOS, charging  $C_L$  to  $V_{DD}$ . The gate enters the evaluate phase when  $\phi$  is logic 1, turning off the PMOS and turning on the NMOS. If the input combination results in a logic 0,  $C_L$  discharges through the NMOS transistors that are turned on so that G = GND; any logic 1 output leaves G  $\approx V_{DD}$ , as  $C_L$  slowly discharges through the load and parasitic resistances. With the two-phase operation,  $P_{Static} = 0$ , as there never exists a path between  $V_{DD}$  and GND. However, it must be assured that the inputs change only during pre-charge. A 0 $\rightarrow$ 1 output transition cannot occur during evaluate, as there exists no connection to  $V_{DD}$  to charge  $C_L$  to logic 1. Because most digital systems are pipelined, it becomes trivial to synchronize the inputs to meet this requirement. With the reduced  $C_L$ ,  $P_{Dynamic}$  is smaller than a CMOS gate, and the speed is improved.  $P_{Dynamic}$  is usually experienced less frequently: only during a 1 $\rightarrow$ 0 transition upon entering evaluate, and a 0 $\rightarrow$ 1 transition entering pre-charge.

Because this gate is synchronous, two major problems non-existent to the other gates presented are introduced. First is the issue of clock skew, when the clock signal arrives at the load gates before arriving at the driver gate [34]. Should the propagation delay of the clock interconnect between the load and driver be equal or greater than the pulse width, the load gates prematurely evaluate the inputs before the driver has actually had a chance to produce those correct inputs. Skew becomes even more significant as clock frequencies increase; therefore, it becomes necessary to have a very carefully designed clock distribution network. The second major problem is with the fundamental concept of a clock distribution network itself. In modernday integrated circuits, clock distribution and communication account for up to 60% of the overall power consumption. The increased power consumption is due to the fact that the transistors of the clock buffers are constantly switching as long as a clock signal is present. When calculating the power consumption of a dynamic gate, it is necessary to include the power consumption of the clock buffer(s) driving the gate. Additionally, assume that the inputs to the dynamic gate are held constant for several clock periods such that G = GND. Consequently, G must swing between  $V_{DD}$  and GND upon entering and exiting pre-charge. Therefore, when averaged over the duration of those clock cycles, the  $P_{Dynamic}$  of this gate is greater than an asynchronous gate whose output remains fixed at GND for the same duration. For a constant logic 1 output, at the end of evaluate, G must swing back to V<sub>DD</sub> due to the charge leakage, although this swing is smaller in magnitude. It becomes possible that the combined power

56

consumption of the gate and clock buffer(s) plus  $P_{Dynamic}$  during idle inputs may exceed the power consumption of an asynchronous logic gate.

Figure 4.3: A dynamic logic implementation of G (right) and the clock driver (left).

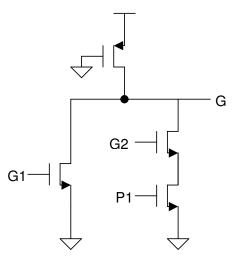

A differential cascode voltage switch (DCVS) gate [35][36], shown in Figure 4.4, attempts to provide the reduced  $C_L$  of pseudo-NMOS and dynamic gates, but with asynchronous operation and no  $P_{Static}$ . The fundamental component is the differential PMOS stack comprised of two identically matched transistors whose gates are driven by the output of the inverse, insuring a purely differential output. Because both pull-down networks must be exactly symmetric, the pull-down function cannot be implemented with the NMOS network used in the previous three gates. G and nG are realized using pass-gate (PG) logic [36], a modified version of pass-transistor logic that prevents floating nodes. No static power dissipation exists for DCVS-PG gates, and  $C_L$  is reduced due to the absence of a complementary pull-up network. Because of the dual logic networks, however,  $P_{Dynamic}$  is expected to be greater than that of a pseudo-NMOS or dynamic gate. Additionally, the total input capacitance is twice as large, and the gates driving G1 and nG1 also experience input resistance. As a result, lower speed operation may be expected.

Figure 4.4: An implementation of G using differential cascode voltage switch pass gate

(DCVS-PG) logic.

### **4.2 Test Procedure**